Программируемые логические интегральные схемы CPLD компании Xilinx

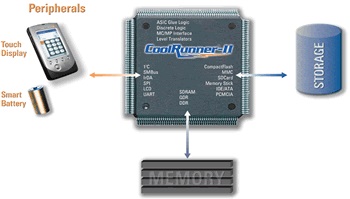

Логические устройства данного типа содержат программируемые макроячейки. Массивы on/off коммутируемы с внешними выводами и внутренними шинами. Набор функциональных возможностей интегральных схем с архитектурой CPLD кодируется в энергонезависимой памяти. Конфигурация сохраняется при отключении питания. Схемы используются в контроллерах COM-портов, USB, VGA. Перепрограммируемый массив может выполнять множество логических функций. Семейство CPLD схем представлено модификациями CoolRunner-II, CoolRunner XPLA3, XC9500XL.

отправка...

отправка...