## Rad-hard adjustable positive voltage regulator

Datasheet - production data

## Features

- Operating input voltage from 3 V to 12 V

- Adjustable output voltage

- 3 A maximum guaranteed output current in SMD5C package, 2 A in FLAT-16

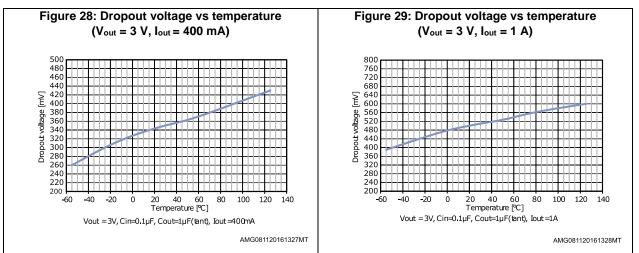

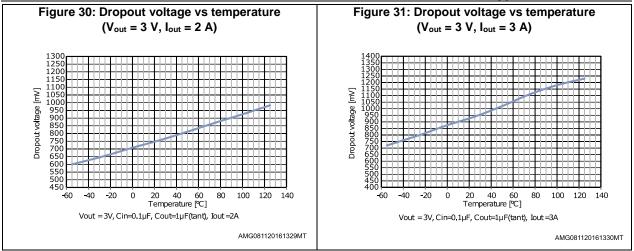

- Very low dropout voltage: 350 mV typ. @ 400 mA

- Embedded overtemperature and overcurrent protection

- Adjustable overcurrent limitation

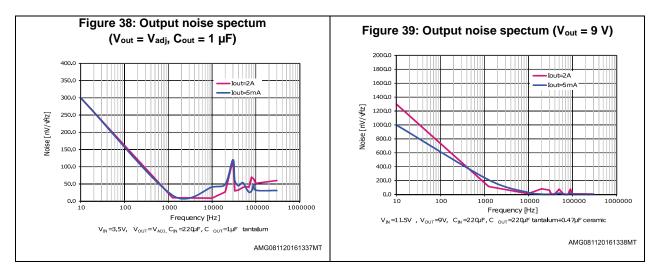

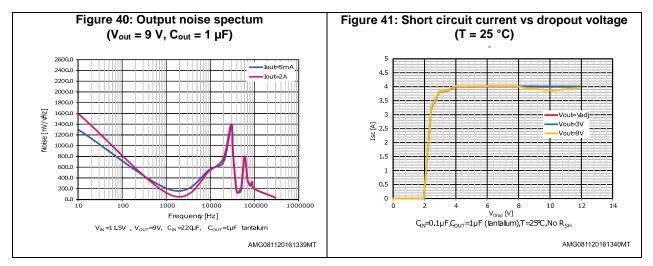

- Very low noise: 40 µV<sub>RMS</sub> (10 Hz-100 kHz)

- Output overload monitoring/signalling

- Inhibit (ON/OFF) TTL-compatible control

- Programmable output short-circuit current

- Remote sensing operation

- Low quiescent current: 1.5 mA typ. @ no load, 150 µA in shutdown

- Rad-hard: guaranteed up to 300 krad Mil Std 883E Method 1019.6 high dose rate and 0.01 rad/s in ELDRS conditions

- Heavy ion, SEL immune.

## Description

The RHFL4913A is a high-performance adjustable positive voltage regulator, able to provide 2 A of maximum current in FLAT-16 package (3 A in the SMD5C package) from an input voltage ranging from 3 V to 12 V, with a typical dropout voltage of 350 mV.

The RHFL4913A features exceptional radiation performances. It is tested in accordance with Mil Std 883E Method 1019.6, in ELDRS conditions. The device is available in the FLAT-16 and the SMD5C hermetic ceramic package, and the QML-V die is specifically designed for space and harsh radiation environments. It operates with an input supply of up to 12 V. The RHFL4913A is QML-V qualified, DSCC SMD #5962F02524.

November 2016

DocID10005 Rev 18

This is information on a product in full production.

### Contents

| Со | ntents   |                                                    |    |

|----|----------|----------------------------------------------------|----|

| 1  | Diagran  | n                                                  | 3  |

| 2  | Pin con  | figuration                                         | 4  |

| 3  | Maximu   | ım ratings                                         | 5  |

| 4  | Electric | al characteristics                                 | 6  |

| 5  | Device   | description                                        | 9  |

|    | 5.1      | ADJ pin                                            | 9  |

|    | 5.2      | Inhibit ON-OFF control                             | 9  |

|    | 5.3      | Overtemperature protection                         | 9  |

|    | 5.4      | Programmable overcurrent protection                | 9  |

|    | 5.5      | OCM pin                                            | 9  |

| 6  | Applica  | tion information                                   | 10 |

|    | 6.1      | Output capacitor selection and stability           | 10 |

|    | 6.2      | Remote sensing operation                           | 11 |

|    | 6.3      | FPGA power supply lines                            | 11 |

|    | 6.4      | Notes on the 16-pin hermetic package               |    |

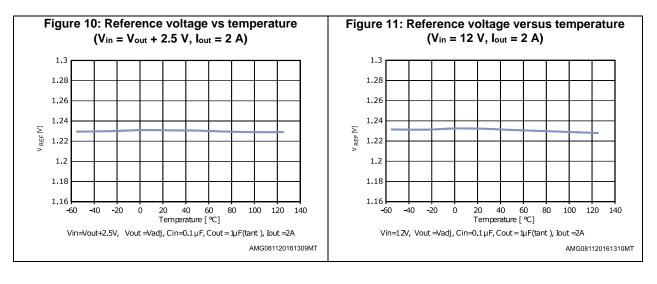

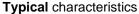

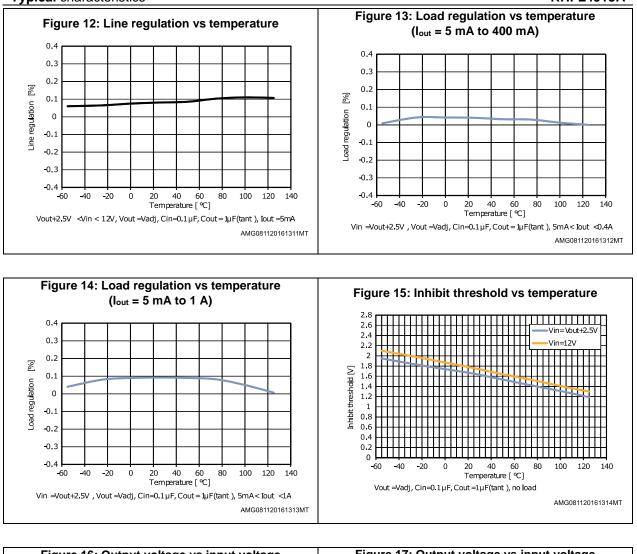

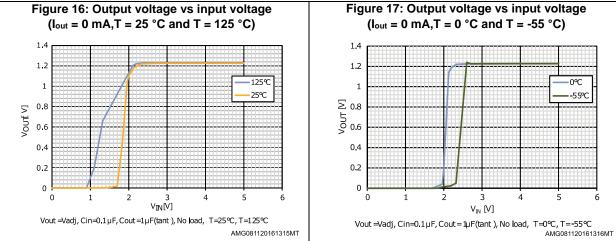

| 7  | Typical  | characteristics                                    | 13 |

| 8  | Die info | prmation                                           | 22 |

|    | 8.1      | Die bonding pad locations and electrical functions | 22 |

| 9  | Packag   | e information                                      | 24 |

|    | 9.1      | FLAT-16 package information                        | 24 |

|    | 9.2      | SMD5C package information                          | 26 |

| 10 | Orderin  | g information                                      | 27 |

| 11 | Revisio  | n history                                          |    |

|    |          | -                                                  |    |

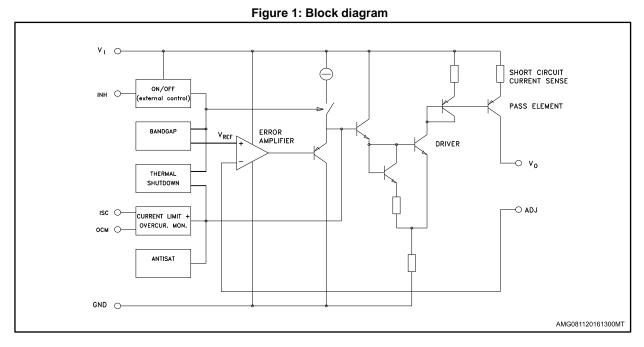

## 1 Diagram

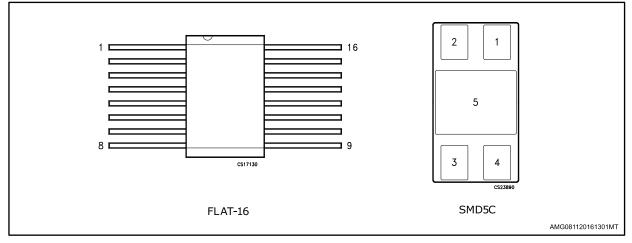

## 2 Pin configuration

Figure 2: Pin configuration (top view for FLAT-16, bottom view for SMD5C)

Table 1: Pin description

| Pin name | FLAT-16 <sup>(1)</sup> | SMD5C <sup>(2)</sup> |

|----------|------------------------|----------------------|

| Vo       | 1, 2, 6, 7             | 1                    |

| Vi       | 3, 4, 5                | 4                    |

| GND      | 13                     | 5                    |

| Isc      | 8                      |                      |

| OCM      | 10                     |                      |

| INHIBIT  | 14                     | 3                    |

| ADJ      | 15                     | 2                    |

| NC       | 9, 11, 12, 16          |                      |

#### Notes:

<sup>(1)</sup>The upper metallic package lid and the bottom metallization are neither connected to regulator die nor to package terminals, hence electrically floating.

<sup>(2)</sup>The upper metallic package lid is neither connected to regulator die nor to package terminals, hence electrically floating.

## 3 Maximum ratings

| Table 2: Recommended | maximum | operating ratings                     |

|----------------------|---------|---------------------------------------|

|                      |         | • • • • • • • • • • • • • • • • • • • |

| Symbol | Parameter                               | Value       | Unit |

|--------|-----------------------------------------|-------------|------|

| VI     | DC input voltage, VI - VGROUND          | 12          | V    |

| Vo     | DC output voltage range                 | 1.23 to 9   | V    |

| lo     | Output current, RHFL4913KPA             | 2           | ^    |

| lo     | Output current,RHFL4913SCA              | 3           | A    |

| PD     | $T_C = 25 \text{ °C}$ power dissipation | 15          | W    |

| Tstg   | Storage temperature range               | -65 to +150 | °C   |

| Тор    | Operating junction temperature range    | -55 to +150 | °C   |

| ESD    | Electrostatic discharge capability      | Class 3     |      |

Exceeding maximum ratings may damage the device.

#### Table 3: Thermal data

| Symbol            | Parameter                                           | Value | Unit |

|-------------------|-----------------------------------------------------|-------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case, FLAT-16 and SMD5C | 8.3   | °C/W |

| T <sub>SOLD</sub> | Maximum soldering temperature, 10 sec.              | 300   | °C   |

## 4 Electrical characteristics

$T_{\rm J}$  = 25 °C,  $V_{\rm I}$  =  $V_{\rm O}$  + 2.5 V,  $C_{\rm I}$  =  $C_{\rm O}$  = 1  $\mu F,$  unless otherwise specified.

Table 4: Electrical characteristics

| Symbol           | Parameter                           | Test conditions                                                                                                           | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VI               | Operating input voltage             | $I_0 = 1 \text{ A},  \text{T}_\text{J} = -55 \text{ to } 125 \ ^\circ\text{C}$                                            | 3    |      | 12   | V    |

|                  |                                     | $I_O = 1 A$ for FLAT-16,<br>2 A for SMD5C,<br>$V_O = V_{ADJ}$                                                             | 1.19 | 1.23 | 1.27 |      |

| Vo               | Output voltage                      | $I_0 = 1 A \text{ for FLAT-16},$<br>2 A for SMD5C,<br>$V_0 = 9 V$                                                         | 8.7  |      | 9.3  | V    |

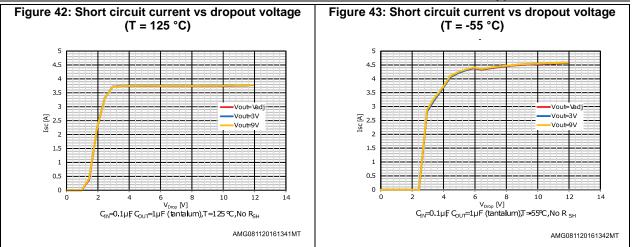

| ISHORT           | Output current limit <sup>(1)</sup> | Adjustable by mask/external resistor                                                                                      | 1    | 4.5  |      | А    |

|                  |                                     | $V_1 = V_0+2.5 V \text{ to } 12 V,$<br>$I_0 = 5 \text{ mA}, T_J = +25 \text{ °C}$                                         |      | 0.07 | 0.35 |      |

|                  |                                     | $V_1 = V_0+2.5 V \text{ to } 12 V,$<br>$I_0 = 5 \text{ mA}, T_J = -55 \ ^\circ\text{C}$                                   |      | 0.05 | 0.4  | 0/   |

| ΔVο/ΔVι          | Line regulation                     | $V_1 = V_0+2.5 V \text{ to } 12 V,$<br>$I_0 = 5 \text{ mA}, T_J = +125 \text{ °C}$                                        |      | 0.1  | 0.4  | %    |

|                  |                                     | $V_{I} = 3 V \text{ to } 12 V,$<br>$I_{O} = 5 \text{ mA}, T_{J} = -55 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}$ |      | 0.1  | 0.5  |      |

|                  |                                     | $V_I = V_O + 2.5 V,$<br>$I_O = 5 \text{ to } 400 \text{ mA}, T_J = +25 \text{ °C}$                                        |      | 0.04 | 0.3  |      |

|                  |                                     | V <sub>I</sub> = V <sub>O</sub> + 2.5 V,<br>I <sub>O</sub> = 5 to 400 mA, T <sub>J</sub> = -55 °C                         |      | 0.02 | 0.5  |      |

|                  |                                     | V <sub>I</sub> = V <sub>O</sub> + 2.5 V,<br>I <sub>O</sub> = 5 to 400 mA, T <sub>J</sub> = +125 °C                        |      | 0.02 | 0.5  |      |

| ΔVο/ΔΙο          | Mo Load regulation                  | $V_{I} = V_{O} + 2.5 V,$<br>Io = 5 mA to 1 A, T <sub>J</sub> = +25 °C                                                     |      | 0.08 | 0.5  | %    |

|                  |                                     | $V_{I} = V_{O} + 2.5 V,$<br>$I_{O} = 5 mA to 1 A, T_{J} = -55 °C$                                                         |      | 0.05 | 0.6  |      |

|                  |                                     | $V_{I} = V_{O} + 2.5 V,$<br>Io = 5 mA to 1 A, T <sub>J</sub> = +125 °C                                                    |      | 0.04 | 0.6  |      |

|                  |                                     | $V_{I} = 3 V,$<br>$I_{O} = 5 \text{ mA to 1 A},$<br>$T_{J} = -55 \text{ °C to +125 °C}$                                   |      | 0.1  | 0.7  |      |

| Z <sub>OUT</sub> | Output impedance                    | $I_{\rm O}$ = 100 mA DC and 20 mA rms                                                                                     |      | 100  |      | mΩ   |

Electrical characteristics

| Symbol              | Parameter                          | Test conditions                                                                                            | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

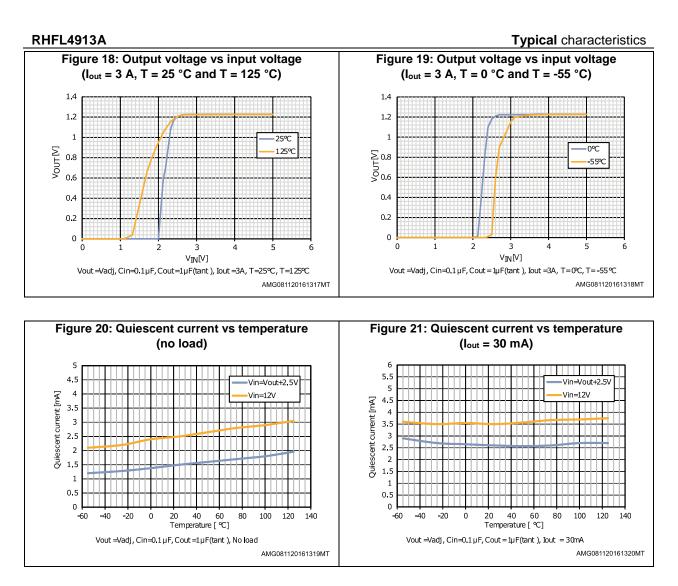

|                     |                                    | $V_{I} = V_{O} + 2.5 V,$<br>$I_{O} = 5 mA,$<br>ON mode (+25 °C)                                            |      | 1.5  | 6    |      |

|                     | Quiescent current                  | $V_{I} = V_{O} + 2.5 V,$<br>$I_{O} = 30 \text{ mA},$<br>ON mode (+25 °C)                                   |      | 2.7  | 8    | ~    |

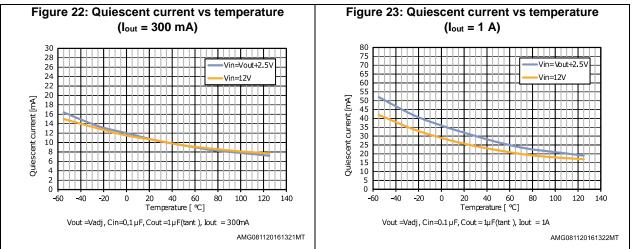

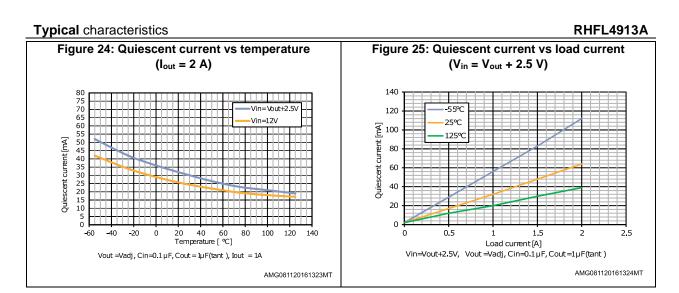

| Iq                  |                                    | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 300 mA,$<br>ON mode (+25 °C)                                                |      | 11   | 25   | mA   |

|                     |                                    | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 1 A,$<br>ON mode (+25 °C)                                                   |      | 32   | 60   |      |

|                     |                                    | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 30 \text{ mA}, (-55 °C)$                                                    |      | 3    | 14   |      |

|                     |                                    | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 300 \text{ mA}, (-55 °C)$                                                   |      | 15   | 40   |      |

|                     | Quiescent current                  | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 1 A, (-55 °C)$                                                              |      | 52   | 100  |      |

| lq                  | ON mode                            | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 30 \text{ mA}, (+125 °C)$                                                   |      | 3    | 8    | mA   |

|                     |                                    | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 300 \text{ mA}, (+125 °C)$                                                  |      | 8    | 20   |      |

|                     |                                    | $V_1 = V_0 + 2.5 V,$<br>$I_0 = 1 A, (+125 °C)$                                                             |      | 20   | 40   |      |

| I <sub>q(off)</sub> | Quiescent current<br>Shutdown mode | $\label{eq:VI} \begin{array}{l} V_{I} = V_{O} + 2 \; V, \\ V_{INH} = 2.4 \; V, \\ OFF \; mode \end{array}$ |      | 0.15 | 1    | mA   |

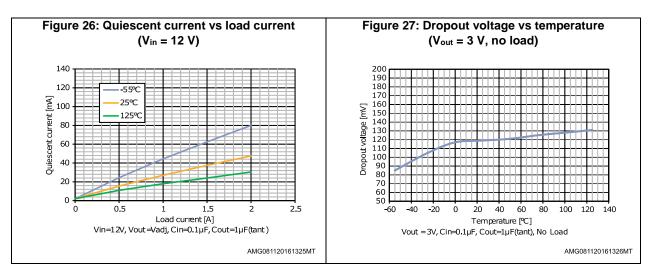

|                     |                                    | Io = 0 mA, Vo = 2.5 V to 9 V                                                                               |      | 130  |      |      |

|                     |                                    | Io = 400 mA,<br>Vo = 2.5 to 9 V, (+25 °C)                                                                  |      | 350  | 450  |      |

|                     |                                    | I <sub>O</sub> = 400 mA,<br>V <sub>O</sub> = 2.5 to 9 V, (-55 °C)                                          |      | 300  | 400  |      |

|                     |                                    | Io = 400 mA,<br>Vo = 2.5 to 9 V, (+125 °C)                                                                 |      | 450  | 550  |      |

| Vd                  | Dropout voltage                    | $I_0 = 1 \text{ A},$<br>V <sub>0</sub> = 2.5 to 9 V, (+25 °C)                                              |      | 500  | 650  | mV   |

|                     |                                    | Io = 1 A,<br>Vo = 2.5 to 9 V, (-55 °C)                                                                     |      | 400  | 550  |      |

|                     |                                    | Io = 1 A,<br>Vo = 2.5 to 9 V, (+125 °C)                                                                    |      | 640  | 800  |      |

|                     |                                    | $I_0 = 2 A,$<br>V <sub>0</sub> = 2.5 to 9 V, (+25 °C)                                                      |      | 750  |      |      |

|                     |                                    | I <sub>O</sub> = 2 A,<br>V <sub>O</sub> = 2.5 to 9 V, (+125 °C)                                            |      | 950  |      |      |

| 57                  |                                    |                                                                                                            |      |      |      | 7/29 |

#### **Electrical** characteristics

#### RHFL4913A

| Symbol       | Parameter                                | Test conditions                                                                                                                |                       | Min.   | Тур. | Max. | Unit  |

|--------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|------|------|-------|

| VINH(ON)     | Inhibit voltage                          | $I_0 = 5 \text{ mA},  \text{T}_\text{J} = -55 \text{ to } +125 \ ^\circ\text{C}$                                               |                       |        |      | 0.8  | V     |

| VINH(OFF)    | Inhibit voltage                          | $I_0 = 5 \text{ mA},  \text{T}_\text{J} = -55 \text{ to } +125 \ ^\circ\text{C}$                                               |                       | 2.4    |      |      | v     |

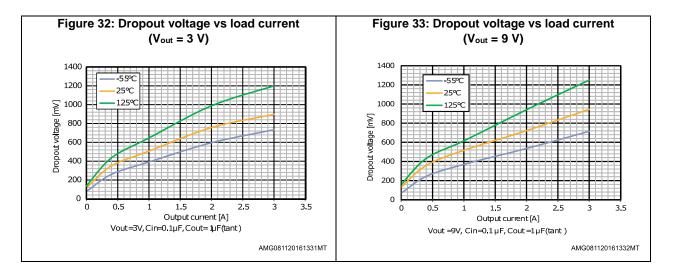

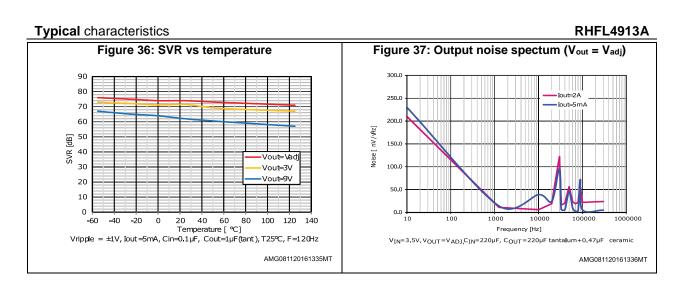

| SVR          | Supply voltage                           | $V_1 = V_0 + 2.5 V \pm 0.5 V$ ,                                                                                                | f = 120 Hz            | 60     | 70   |      | ٩D    |

| SVK          | rejection <sup>(1)</sup>                 | Vo = 3 V, Io = 5 mA                                                                                                            | f = 33 KHz            | 30     | 40   |      | dB    |

| Isн          | Shutdown input<br>current                | V <sub>INH</sub> = 5 V                                                                                                         |                       |        | 15   |      | μA    |

| Vосм         | OCM pin voltage                          | Sinked I <sub>OCM</sub> = 24 mA active low                                                                                     |                       |        | 0.38 |      | V     |

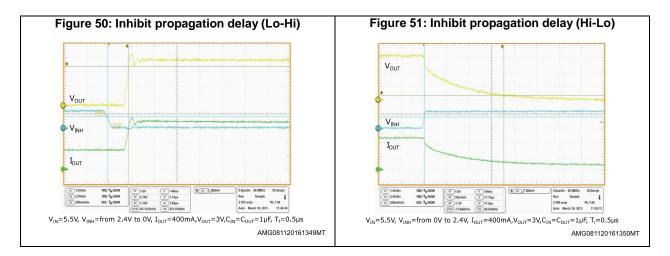

|              |                                          | $V_1 = V_0 + 2.5 V,$                                                                                                           |                       | ON-OFF |      | 20   | μs    |

| tplh<br>tphL | Inhibit propagation delay <sup>(1)</sup> | $\begin{split} V_{\text{INH}} &= 2.4 \text{ V}, \\ I_{\text{O}} &= 400 \text{ mA}, \\ V_{\text{O}} &= 3 \text{ V} \end{split}$ |                       | OFF-ON |      | 100  | μs    |

| eN           | Output noise voltage <sup>(1)</sup>      | B = 10 Hz to 100 kHz,<br>$I_0 = 5$ mA to 2 A                                                                                   | B = 10 Hz to 100 kHz, |        | 40   |      | µVrms |

#### Notes:

<sup>(1)</sup>These values are guaranteed by design. For each application it is strongly recommended to comply with the maximum current limit of the package used.

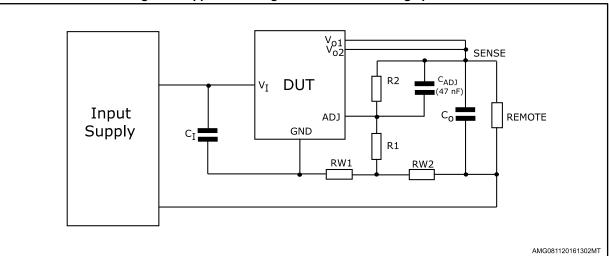

### Figure 3: Application diagram for remote sensing operation

## 5 Device description

The RHFL4913A adjustable voltage regulator contains a PNP type power element controlled by a signal resulting from an amplified comparison between the internal temperature-compensated band-gap and the fraction of the desired output voltage value obtained from an external resistor divider bridge. The device is protected by several functional blocks.

### 5.1 ADJ pin

The load output voltage feedback comes from an external resistor divider bridge mid-point connected to the ADJ pin (allowing all possible output voltage settings as per user requirements) established between load terminals.

### 5.2 Inhibit ON-OFF control

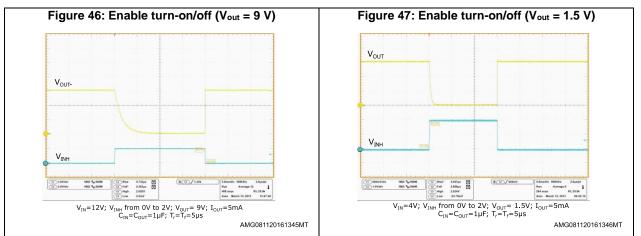

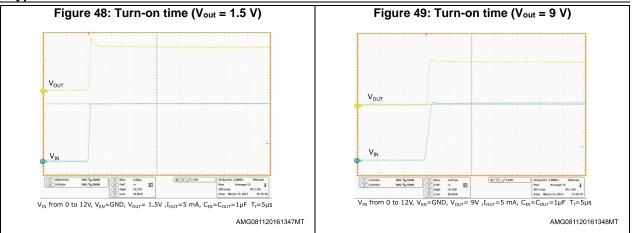

By setting the INHIBIT pin TTL high, the device switches off the output current and voltage. The device is ON when the INHIBIT pin is set low. Since the INHIBIT pin is pulled down internally, it can be left floating in cases where the inhibit function is not used.

### 5.3 Overtemperature protection

A temperature detector internally monitors the power element junction temperature. The device turns off when a temperature of approximately 175 °C is reached, returning to ON mode when back to approximately 135 °C. Combined with the other protection blocks, the device is protected from destructive junction temperature excursions in all load conditions. It should be noted that when the internal temperature detector reaches 175 °C, the active power element can be as high as 225 °C. Prolonged operation under these conditions far exceeds the maximum operating ratings and device reliability cannot be guaranteed.

## 5.4 **Programmable overcurrent protection**

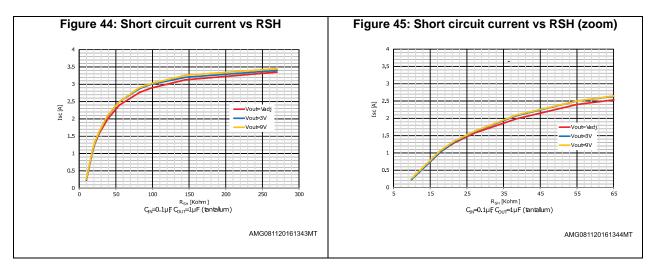

An internal non fold-back short circuit limitation is set with  $I_{SHORT} > 3.8 \text{ A}$  (V<sub>0</sub> is 0 V). This value can be decreased via an external  $R_{SH}$  resistor connected between the  $I_{SC}$  and  $V_I$  pins, with a typical value range of 10 k $\Omega$  to 200 k $\Omega$  (refer to *Figure 44: "Short circuit current vs RSH"* and *Figure 45: "Short circuit current vs RSH"* (zoom)").To maintain optimal  $V_0$  regulation, it is necessary to set  $I_{SHORT}$  1.6 times greater than the maximum desired application I<sub>0</sub>. When I<sub>0</sub> reaches  $I_{SHORT}$  – 300 mA, the current limiter overrules the regulation,  $V_0$  starts to drop and the OCM flag is raised. When no current limitation adjustment is required, the  $I_{SC}$  pin must be left unbiased (as it is in 3 pin packages).

## 5.5 OCM pin

The OCM pin goes low when the current limit becomes active, otherwise  $V_{OCM} = V_I$ . It is buffered and can sink 10 mA. The OCM pin is internally pulled up by a 5 k $\Omega$  resistor.

## 6 Application information

To adjust the output voltage, the R2 resistor must be connected between the  $V_0$  and ADJ pins. The R1 resistor must be connected between ADJ and ground. Resistor values can be derived from the following formula:

$V_0 = V_{ADJ} (R1 + R2) / R1$

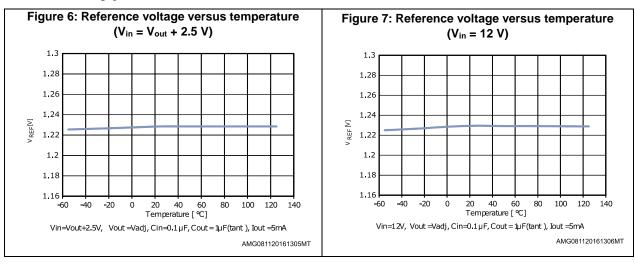

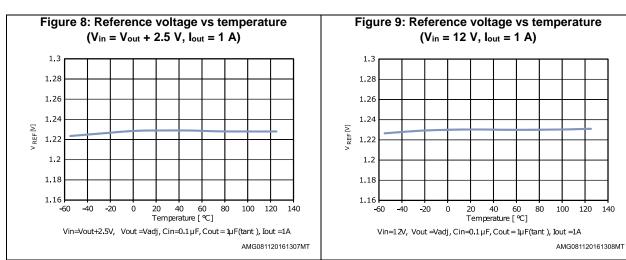

The  $V_{\text{ADJ}}$  is typically 1.23 V, controlled by the internal temperature-compensated band gap block.

The minimum input voltage is 3 V. The RHFL4913A adjustable is functional as soon as the V<sub>I</sub> - V<sub>O</sub> voltage difference is slightly above the power element saturation voltage. The adjust pin to ground resistor (R1) value must not be greater than 10 k $\Omega$ , in order to keep the output feedback error below 0.2 %. A minimum of 0.5 mA I<sub>O</sub> must be set to ensure perfect no-load regulation. It is advisable to dissipate this current into the divider bridge resistor.

All available  $V_1$  pins, as well as all available  $V_0$  pins, should always be externally interconnected, otherwise the stability and reliability of the device cannot be guaranteed.

The inhibit function switches off the output current electronically, and therefore very quickly. According to Lenz's law, external circuitry reacts with Ldl/dt terms which can be of high amplitude in case somewhere a serial coil inductance exists. Large transient voltage would develop on both device terminals. It is advisable to protect the device with Schottky diodes to prevent negative voltage excursions. In the worst case, a 14 V Zener diode could protect the device input.

Since the RHFL4913A adjustable voltage regulator is manufactured with very high speed bipolar technology (6 GHz f<sub>T</sub> transistors), the PCB layout must be designed with exceptional care, with very low inductance and low mutually coupling lines. Otherwise, high frequency parasitic signals may be picked up by the device resulting in system self-oscillation. The benefit is an SVR performance extended to far higher frequencies.

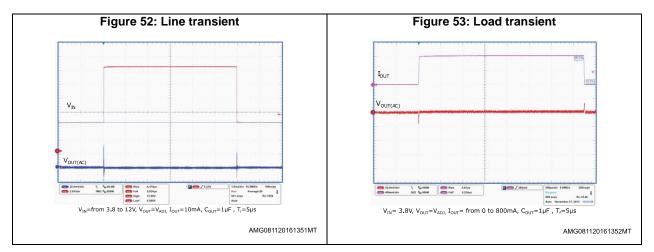

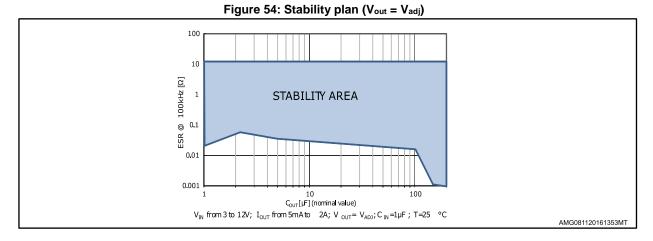

## 6.1 Output capacitor selection and stability.

The device has been designed for high stability and low dropout operation.

To ensure regulator stability, input and output capacitors with a minimum 1  $\mu$ F are mandatory. When large transient currents are expected, larger value capacitors are necessary. The detailed stability plane versus output capacitance and ESR is shown in *Figure 54:* "*Stability plan* (*Vout* = *Vadj*)".

In the case of high current operation with short circuit events expected, caution must be exercised with regard to capacitors. They must be connected as close as possible to the device terminals. As some tantalum capacitors may permanently fail when subjected to high charge-up surge currents, it is recommended to decouple them with 470 nF polyester capacitors.

### 6.2 Remote sensing operation

A separate kelvin voltage sensing line provides the ADJ pin with exact load "high potential" information (see *Figure 3: "Application diagram for remote sensing operation"*). But variable remote load current consumption induces variable lq current (lq is roughly the l<sub>o</sub> current divided by the  $h_{FE}$  of the internal PNP series power element) routed through the parasitic series line resistor RW2. To compensate for this parasitic voltage, resistor RW1can be introduced to provide the necessary compensating voltage signal to the ADJ pin.

A ceramic or poliester 47nF  $C_{ADJ}$  capacitor between ADJ and  $V_{OUT}$  pins is recommended when the remote sensing technique is implemented.

### 6.3 FPGA power supply lines

Because FPGA devices are very sensitive to  $V_{DD}$  transients beyond a few % of their nominal supply voltage (usually 1.5 V), special attention must be given by supply lines designers to mitigate possible heavy ion disturbances. The worst case heavy ion effect can be summarized as: the RHFL4913 internal control loop being cut (made open) or shortcircuited for a sub-microsecond duration. During such an event, the RHFL4913 power element can either provide excessive current or current supply stoppage to the output (V<sub>OUT</sub>) for a duration of about one microsecond, after which time the RHFL4913 smoothly recovers to nominal operation.

According to the simulations, some very short SET (i.e. those having duration < 100 nsec) are dependent also on the stray inductances related to the PCB topology, especially those on the ground.

To mitigate these "transients", it is recommended to implement the RHFL4913 PCB layout as follows:

- Minimizing series/parallel parasitic inductances of the PCB path

- Using an effective grounding scheme with short connections to GND, such as a starbus topology, whose board GND is at the GND force. The best solution is a ground plane.

- Using a low ESR 47 µF C<sub>OUT</sub> filtering capacitor, with ESR lower than 30 mΩ, together with a 470 nF ceramic capacitor in parallel (to reduce dynamic ESR)

- Implementing the SET mitigation circuit, by adding additional filtering components as described in *Figure 4: "Baseline bias configuration with remote feedback"* and *Figure 5: "Local feedback configuration"*.

With this implementation, the ELDO simulated worst transient case shows no more than 90 mV deviation from the nominal line voltage value.

Additional details and suggestions regarding the application techniques aimed to mitigate the SET effects on a linear voltage regulator can be found in the AN2984 ("Minimizing the SET-related effects on the output of a voltage linear regulator, available on www.st.com).

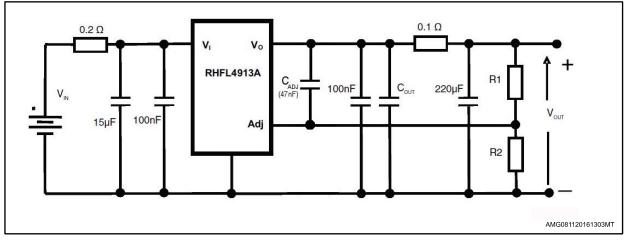

### Figure 4: Baseline bias configuration with remote feedback

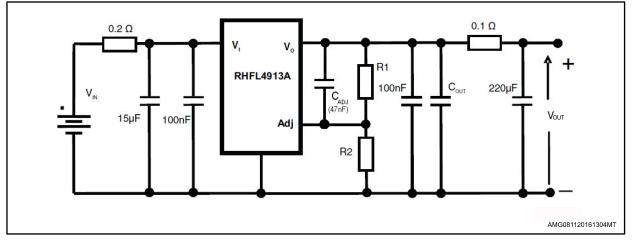

### Figure 5: Local feedback configuration

## 6.4 Notes on the 16-pin hermetic package

The bottom section of the 16-pin package is metallized in order to allow the user to directly solder the RHFL4913A onto PCB, no heat sink needed for enhanced heat removal.

7

## Typical characteristics

DocID10005 Rev 18

57

RHFL4913A

Typical characteristics

Typical characteristics

Typical characteristics

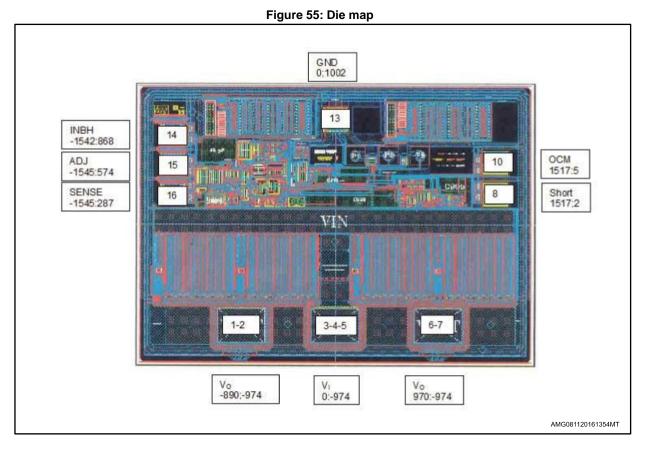

## 8 Die information

Pad numbers reflect terminal numbers when placed in case FLAT-16.

## 8.1 Die bonding pad locations and electrical functions

Die physical dimensions:

- Die size: 150 mils x 110 mils (3.81 mm by 2.79 mm)

- Die thickness:  $375 \ \mu m \pm 25 \ \mu m$  (14.8 mils  $\pm 1 \ mil$ )

Pad size: VIN, VOUT pads: 450  $\mu$ m x 330  $\mu$ m (17.7 mils by 13 mils)

Control pads: 184 μm x 184 μm (7.25 mils square)

Interface materials:

- Top metallization: Al/Si/Cu, 1.05 μm ± 0.15 μm

- Backside metallization: none

Glassivation:

- Type: p. vapox + nitride

- Thickness: 0.6 μm ± 0.1 μm + 0.6 μm ± 0.08 μm

Substrate:

• bare silicon

Assembly related information:

- Substrate potential: floating recommended to be tied to ground.

- Special assembly instructions: "Sense" pad not used; not internally connected to any part of the IC. Can be connected to ground when space anti-static electricity rules apply.

## 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

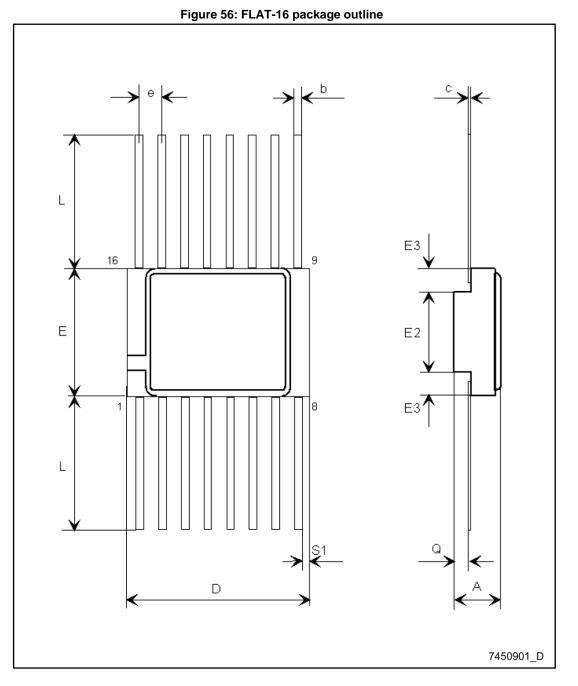

## 9.1 FLAT-16 package information

### Package information

| i donago mormation |                     |                       |       |  |  |

|--------------------|---------------------|-----------------------|-------|--|--|

|                    | Table 5: FLAT-16 pa | ckage mechanical data |       |  |  |

| Dim                | mm                  |                       |       |  |  |

| Dim.               | Min.                | Тур.                  | Max.  |  |  |

| A                  | 2.42                |                       | 2.88  |  |  |

| b                  | 0.38                |                       | 0.48  |  |  |

| С                  | 0.10                |                       | 0.18  |  |  |

| D                  | 9.71                |                       | 10.11 |  |  |

| E                  | 6.71                |                       | 7.11  |  |  |

| E2                 | 3.30                | 3.45                  | 3.60  |  |  |

| E3                 | 0.76                |                       |       |  |  |

| e                  |                     | 1.27                  |       |  |  |

| L                  | 6.35                |                       | 7.36  |  |  |

| Q                  | 0.66                |                       | 1.14  |  |  |

| S1                 | 0.13                |                       |       |  |  |

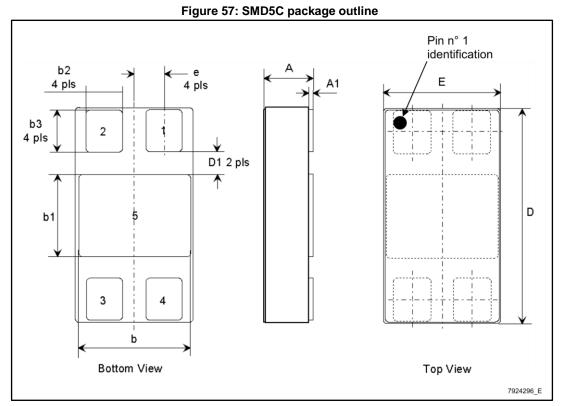

## 9.2 SMD5C package information

### Table 6: SMD5C package mechanical data

| Dim  |       | mm    |       |

|------|-------|-------|-------|

| Dim. | Min.  | Тур.  | Max.  |

| A    | 2.99  | 3.15  | 3.30  |

| A1   | 0.25  | 0.38  | 0.51  |

| b    | 7.13  | 7.26  | 7.39  |

| b1   | 4.95  | 5.08  | 5.21  |

| b2   | 2.28  | 2.41  | 2.54  |

| b3   | 2.92  | 3.05  | 3.18  |

| D    | 13.71 | 13.84 | 13.97 |

| D1   | 0.76  |       |       |

| E    | 7.39  | 7.52  | 7.65  |

| e    |       | 1.91  |       |

## 10 Ordering information

| Table 7: Order codes |                 |                |                 |                |               |  |

|----------------------|-----------------|----------------|-----------------|----------------|---------------|--|

| Die                  | FLAT-16         | SMD5C          | Terminal finish | Output voltage | Quality level |  |

|                      | RHFL4913KPA-01V | RHFL4913SCA07V | Gold            | Adj            | QML-V         |  |

|                      | RHFL4913KPA-02V |                | Solder          | Adj            | QML-V         |  |

|                      | RHFL4913KPA1    | RHFL4913SCA1   | Gold            | Adj            | EM1           |  |

| L4913ADIE2V          |                 |                |                 | Adj            | QML-V die     |  |

| L4913ADIES           |                 |                |                 | Adj            | EM1 die       |  |

### Table 8: Part numbers - SMD equivalent

| ST part number  | SMD part number |

|-----------------|-----------------|

| RHFL4913KPA-01V | 5962F0252401VXC |

| RHFL4913KPA-02V | 5962F0252401VXA |

| RHFL4913SCA07V  | 5962F0252403VUC |

| L4913ADIE2V     | 5962F0252401V9A |

#### Table 9: Environmental characteristics

| Parameter                      | Conditions                                          | Value | Unit     |

|--------------------------------|-----------------------------------------------------|-------|----------|

| Output voltage thermal drift   | -55°C to +125°C                                     | 40    | ppm/°C   |

| Output voltage radiation drift | From 0 krad to 300 krad at 0.55 rad/s               | 8     | ppm/krad |

| Output voltage radiation drift | From 0 krad to 300 krad, Mil Std 883E Method 1019.6 | 6     | ppm/krad |

## 11 Revision history

Table 10: Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29-Oct-2004 | 3        | New order codes added - Tables 4 and 5.                                                                                                                                                                                                  |  |

| 27-May-2005 | 4        | Features, Tables 4, 5 and the Figure 1 has been updated. Add the Mechanical Data SOC-16.                                                                                                                                                 |  |

| 08-Jun-2005 | 5        | Mistake on Table 4 (Q.ty Level), Table 7 has been updated and add DIE Information                                                                                                                                                        |  |

| 30-Jan-2006 | 6        | Added new package SMD5C and removed old package SOC-16.                                                                                                                                                                                  |  |

| 26-Jan-2007 | 7        | DIE Information and DIE Pad has been updated par. 6, pages 9 and 10.                                                                                                                                                                     |  |

| 23-Nov-2007 | 8        | Pin information for the SMD5C package updated in Table 1; added section 6.3: FPGA power supply lines on page 10. Minor text changes.                                                                                                     |  |

| 22-Sep-2008 | 9        | Modified Application information on page 9.                                                                                                                                                                                              |  |

| 17-Nov-2008 | 10       | Modified Table 8 on page 26.                                                                                                                                                                                                             |  |

| 21-Jan-2010 | 11       | Modified Table 7 on page 26.                                                                                                                                                                                                             |  |

| 18-Oct-2010 | 12       | Modified Section 6.2 on page 9.                                                                                                                                                                                                          |  |

| 07-Feb-2011 | 13       | Added: note Table 1 on page 3.                                                                                                                                                                                                           |  |

| 07-Dec-2011 | 14       | Removed the note under Table 1 on page 3 and added footnotes 1 and 2.                                                                                                                                                                    |  |

| 20-Aug-2012 | 15       | Order code updated in Table 7 on page 26 about the SMD5C package                                                                                                                                                                         |  |

| 15-Jan-2014 | 16       | Updated Features in cover page.<br>Added Section 7: Typical characteristics.<br>Modified Table 4: Electrical characteristics.<br>Updated Section 9: Package mechanical data and Section 10: Ordering information.<br>Minor text changes. |  |

| 05-May-2014 | 17       | Updated Figure 18: Output voltage vs input voltage<br>(I <sub>out</sub> =3 A, T=25 °C and T=125 °C).<br>Minor text changes.                                                                                                              |  |

| 22-Nov-2016 | 18       | Updated description in cover page.<br>Updated Section 9: "Package information".<br>Minor text changes.                                                                                                                                   |  |

\_\_\_\_\_

#### **IMPORTANT NOTICE – PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved